# Consideration of Net Weights for Performance **Driven Routing**

Geetanjali Udgirkar, G. Indumathi

Abstract: Objectives: In todays' VLSI technology, interconnect delay is the predominant factor in determining the speed of the final chip. Considering the complexity and size of today's VLSI designs, timing driven VLSI routing is very challenging problem.

Methods/Statistical analysis: The obvious method is to assign weights to the nets of a given route and perform timing driven There are few works in the literature on net-weighting-based timing driven routing. Findings: Based on the criticality of the nets, by assigning weights to the nets in two methods discussed in the paper, we present two novel timing driven routing algorithms. In the first method, a constant is raised to the power of a variable exponent for weight assignment, whereas, in the second method, a variable exponent is raised to the power of a constant. These weights are considered during timing driven VLSI routing for an FPGA using VPR routing tool. Improvements: The proposed methods show significant improvement in timing over VPR routing tool. We obtain improvement of 14.65% and 26.85% using the methods MethodA and MethodB respectively, over VPR.

Keywords: VLSI Routing, Global Routing, Net Weighting Method.

## I. INTRODUCTION

According to Moore's law the gate count increases twice every year. As more and more cells are added to the design, placement and routing complexity of the design increases many folds. This is primarily due to the fact that the interconnect delay becomes significant. The efficient placement and routing of the design decides the performance of the final chip. Many methods have been proposed in the literature at the level of placement of the design and also at the global routing level to address this issue. In this paper, we focus on methods to perform efficient timing driven global routing for FPGA based designs.

Timing optimization algorithms have been traditionally applied to placement problems. There are two types of approaches in the placement and routing methods, 1) Path based and 2) Net based. In path-based approaches, the critical path of the design under consideration are analyzed and optimized. These approaches are complex to analyze and difficult to implement which is primarily due to exponential number of paths in a design. Net based methods are easy to implement compare to path-based approaches and hence are very popular. Weights of nets are computed based on the

Manuscript published on 28 February 2019.

Correspondence Author (s)

Geetanjali Udgirkar, CMR Institute of Technology, Bangalore, Karnataka, India

Dr. G. Indumathi, Cambridge Institute of Technology, Bangalore

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license http://creativecommons.org/licenses/by-nc-nd/4.0/

criticality of the net in the design, and then these weights are applied during the run of the routing tool.

Resources present in FPGA routing architecture use segments of various lengths. Due to this reason, the traditional (as in ASIC) methods of route length estimation do not apply. Timing driven routing becomes even more difficult under such scenario. In this paper we investigate the net weighing schemes for FPGA based designs. Our approach in this paper is based on application of weights to the critical nets during the global routing flow. We use VPR tool for our experiments with a number of FPGA designs.

Peishan Tu et al.[1] proposed a novel timing driven routing tree construction method for tradeoff between wirelength and timing. Their approach is based on shortest path trees and minimum spanning trees.

Dongsheng Wang et al.[2], proposed a method in which graph connectivity of graph is obtained at first which is based on observing Elmore delay model. This graph is known as DCG (directed connectivity graph) which describes connectivity of all the edges of the graph. They also propose a C-Tree algorithm which is a timing-driver Steiner tree routing approach. Dongsheng Wang et al.[3] propose a new algorithm called MCM/IC multilayer routing algorithm, named MLR, which is timing driven and considers the Elmore delay as a performance issue. It also consider number of layers, total wirelength and the vias. Based on layer assignment problem, this algorithm assigns all the nets into the routing layers in a layer-pair by later-pair fashion.

Jin-Tai Yan et al.[4], proposes a simulated-annealing based approach, wherein, the input is an initial routing tree. They consider routing flexibility in a SRT and flexibility of the Steiner-point in one Y-type wire. The flexibility of the points is timing constrained. The simulated-annealing-based approach obtains better timing-constrained a flexibility-driven SRT by performing reassignment of the possible locations of the Steiner points in a SRT.

Tsung-Yi Ho et al.[5], propose a new framework for rapid multilevel routing considering performance optimization and crosstalk. To optimize performance-driven routing, they have proposed a new method of minimum-radius minimum-cost spanning tree algorithm which is applied in global routing. To reduce the crosstalk problem, they have added an intermediate stage of layer/track into their routing framework. Fang-Jou Liu et al.[6] propose a novel timing model which is based on the layout of the design. This is based on Asymptotic Waveform Evaluation (AWE) which helps in analysis of timing paths during global routing. This computation of moments of the interconnect tree are enabled by this model in a bottom-up fashion, and can be integrated global router without much effort.

## **Consideration of Net Weights for Performance Driven Routing**

This integration helps in layout optimization in an incremental manner, i.e., routing and timing analysis are performed simultaneously, along with exchange of information between them.

Jiang Hu et al.[7], propose a method for global routing that can optimize routing delay, routing congestion, and number of bends. This approach solves problems which are competing objectives. Based on the timing constraints, routing flexibilities are obtained and used to reduce congestion given the timing constraints.

Kaushik Roy et al.[8], proposes a solution for the problem of place and route in field programmable gate arrays (FPGA's) targeted for low power dissipation constrained by critical path delays. There is a capacitive loading for each net of the large number of unprogrammed anti-fuses present in the routing architecture. Due to signal transitions happening at the output of logic gates, a substantial amount of power gets dissipated in the routing architecture. The signal transitions within internal nodes of the circuit are estimated based on primary input signal distributions.

Jucemar Monteiro et al.[9], proposed an algorithm in which both routing metrics and timing are considered during detailed placement. They also present a detailed analysis of a score for the timing quality and the number of routing overflows. They also provide a trade-off between them and experiment their algorithm on the International Conference on Computer Aided Design (ICCAD) 2015 timing-driven contest benchmarks.

Hsiao-Ping Tseng et al.[20], propose a crosstalk and timing driven router for the task of VLSI design which is used for detailed and global routing. This method targets to process the timing constraints and crosstalk by tuning wire spacing and by performing ordering of nets and by quantitative analysis. This novel heuristic fits for detailed routing and global routing along with the flow of layout design.

Takahiro DEGUCHI et al.[11], present a method for performance driven routing. This method is based on a multi-layer routing model. The use linear programming in this method by considering buffer insertion and wire sizing under timing constraints. The routes for each net are determined in a hierarchical level.

Sung-Woo Hur et al.[12], this paper performs the study of the performance driven objective of maze routing. They adopt a graph model appropriate for applications to global and detailed routing. This model captures blockages naturally, limits the routing layer assignment and wire-sizing resources. The perform annotation of each edge in the graph with capacitance and resistance values pertaining to the particular wire segment. The objective is to find low resistance-capacitance delay paths or obtains a tradeoff between total capacitance and resistance-capacitance delay.

Jin-Tai Yan et al.[13] present a method for performance driven routing which is based upon the concept of assignment of hidden Steiner points and insertion of sharing buffer. This is achievable for input graph where a set of connecting nodes of a net are given. They construct a rectilinear Steiner tree which is performance driven by inserting Steiner points and

sharing buffers into all possible positions that given a better performance.

Christophe Alexandre et al.[14], propose a routing tool called TSUNAMI, which is more of a platform based on an C++ database. All the tools interact with this database consistently and collaborate on the problems at hand. A timing driven global routing and a timing driven placement tool has been developed on this platform.

In Section 2, we discuss the implementation aspects of the proposed routing tool. Experiments are presented in Section 3. Finally, we present the results of our approach in Section 3 which is followed by Conclusion in Section 4.

## 2. IMPLEMENTATION OF THE ROUTER

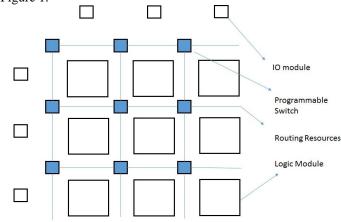

We implement timing driven routing for FPGA routing architecture. A typical FPGA routing architecture is show in Figure 1.

Figure 1: Typical FPGA Resources

Our work is based on the framework of VPR. We implement net weighing algorithms within the framework of VPR. Source code of VPR is modified to implement net weighing schemes A and B. In method A, as shown in Figure 2, we traverse through all the nets of the design, which is followed by traversal for all the pins for each net. In line 1 we compute the Pin<sub>crit</sub> for each pin which is maximum of the ration of net slack divided by time period of the critical path of the design. Next, we assign Pin<sub>crit</sub> to be equal to 10 raised to the power of Pin<sub>crit</sub>. After this we choose the maximum of Max<sub>criticality</sub> and Pin<sub>crit</sub>.

#### Algorithm 1 Method A for weighting nets 1: for All nets n do 2: for All pins p of net n do $pin\_crit = max((max\_criticality - net\_slack[p]) / T\_crit, 0)$ 3: $pin\_crit = pow(e, pin\_crit)$ 4:

pin\_criticality[p] = pin\_crit 5:

end for 6. 7: end for

Figure 2: Method A

In method B, as shown in Figure 3, in line 1 we assign Pin<sub>crit</sub> to be equal to Pin<sub>crit</sub> raised to the power of 10. After this we choose the maximum of Max<sub>criticality</sub> and Pin<sub>crit</sub>. Then we assign pin\_criticality to variable Pincrit.

```

Algorithm 2 Method B for weighting nets

1: for All nets n do

2:

for All pins p of net n do

pin\_crit = max((max\_criticality - net\_slack[p]) / T\_crit, 0)

3:

pin_crit = pow(pin_crit, e)

4:

pin_criticality[p] = pin_crit

5:

6:

end for

7: end for

```

Figure 3: Method B

## 3. EXPERIMENTS AND RESULTS

We carry out our experiments on twenty FPGA designs. The experiments are run on a 64-bit MAC running on UNIX operating system. We used VPR version 2.4 from internet.

The results obtained by using method A and method are shown in Table 1 and Table 2 respectively. As shown in Table 1, the third column represents the time period for each design, and column 4 and column 5 represent the time period obtained in timing analysis after running the router VPR and the proposed methods respectively.

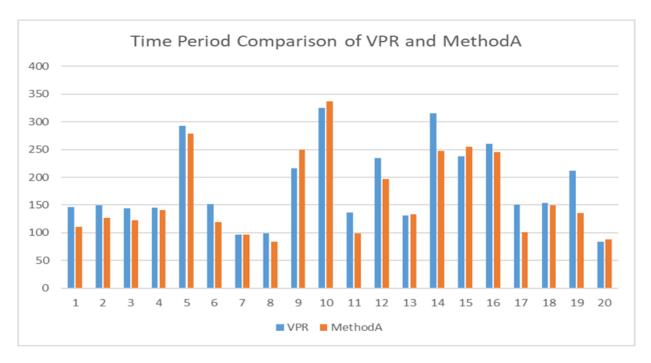

The comparison of time periods obtained for VPR and proposed method (Method A and Method B) are shown in Figure 4 and Figure 5 respectively. Note that while extracting the results for VPR we have used criticality exponent as 0.01 for VPR.

Table 1 Comparison of time period between VPR and proposed for Method A

| Index | Designs  | Clock<br>Period in<br>nanosecond | Period VPR in nanosecond | Period of<br>MethodA in<br>nanosecond | % Improvement in Slack |

|-------|----------|----------------------------------|--------------------------|---------------------------------------|------------------------|

| 1     | alu4     | 82.00                            | 146.491                  | 110.43                                | 43.97683               |

| 2     | apex2    | 130.00                           | 149.168                  | 126.73                                | 17.26                  |

| 3     | apex4    | 150.00                           | 144.419                  | 121.98                                | 14.95933               |

| 4     | bigkey   | 100.00                           | 144.95                   | 141.22                                | 3.73                   |

| 5     | clma     | 300.00                           | 292.266                  | 278.407                               | 4.619667               |

| 6     | des      | 120.00                           | 151.944                  | 118.95                                | 27.495                 |

| 7     | diffeq   | 100.00                           | 96.4889                  | 97.154                                | -0.6651                |

| 8     | dsip     | 65.00                            | 98.5863                  | 83.45                                 | 23.28662               |

| 9     | elliptic | 150.00                           | 215.927                  | 250.144                               | -22.8113               |

| 10    | ex1010   | 189.00                           | 324.849                  | 336.741                               | -6.29206               |

| 11    | ex5p     | 150.00                           | 136.444                  | 98.34                                 | 25.40267               |

| 12    | frisc    | 150.00                           | 234.588                  | 196.601                               | 25.32467               |

| 13    | misex3   | 120.00                           | 131.223                  | 133.561                               | -1.94833               |

| 14    | pdc      | 380.00                           | 315.524                  | 247.065                               | 18.01553               |

## **Consideration of Net Weights for Performance Driven Routing**

| 15      | s298     | 250.00 | 237.959 | 255.431 | -6.9888  |

|---------|----------|--------|---------|---------|----------|

| 16      | s38417   | 125.00 | 260.179 | 244.969 | 12.168   |

|         |          |        |         |         |          |

| 17      | s38584.1 | 91.00  | 150.017 | 101.1   | 53.75495 |

| 18      | seq      | 140.00 | 153.597 | 149.459 | 2.955714 |

| 19      | spla     | 120.00 | 212.304 | 135.31  | 64.16167 |

| 20      | tseng    | 80.00  | 84.2235 | 88.5287 | -5.3815  |

|         |          |        |         |         |          |

| Average |          |        |         |         | 14.65118 |

Table 2 Comparison of time period between VPR for Method B

| Table 2 Comparison of time period between VFK for Method B |          |            |               |            |               |  |  |  |

|------------------------------------------------------------|----------|------------|---------------|------------|---------------|--|--|--|

| Index                                                      | Designs  | Clock      | Period VPR in | Period of  | % Improvement |  |  |  |

|                                                            |          | Period in  | nanosecond    | MethodB in | in Slack      |  |  |  |

|                                                            |          | nanosecond |               | nanosecond |               |  |  |  |

| 1                                                          | alu4     | 82.00      | 146.491       | 110.43     | 43.97683      |  |  |  |

| 2                                                          | apex2    | 130.00     | 149.168       | 126.73     | 17.26         |  |  |  |

| 3                                                          | apex4    | 150.00     | 144.419       | 121.98     | 14.95933      |  |  |  |

| 4                                                          | bigkey   | 100.00     | 144.95        | 141.22     | 3.73          |  |  |  |

| 5                                                          | clma     | 300.00     | 292.266       | 253.611    | 12.885        |  |  |  |

| 6                                                          | des      | 120.00     | 151.944       | 118.95     | 27.495        |  |  |  |

| 7                                                          | diffeq   | 100.00     | 96.4889       | 88.2141    | 8.2748        |  |  |  |

| 8                                                          | dsip     | 65.00      | 98.5863       | 83.45      | 23.28662      |  |  |  |

| 9                                                          | elliptic | 150.00     | 215.927       | 182.579    | 22.232        |  |  |  |

| 10                                                         | ex1010   | 189.00     | 324.849       | 247.535    | 40.90688      |  |  |  |

| 11                                                         | ex5p     | 150.00     | 136.444       | 98.34      | 25.40267      |  |  |  |

| 12                                                         | frisc    | 150.00     | 234.588       | 168.839    | 43.83267      |  |  |  |

| 13                                                         | misex3   | 120.00     | 131.223       | 106.322    | 20.75083      |  |  |  |

| 14                                                         | pdc      | 380.00     | 315.524       | 238.912    | 20.16105      |  |  |  |

| 15                                                         | s298     | 250.00     | 237.959       | 198.24     | 15.8876       |  |  |  |

| 16                                                         | s38417   | 125.00     | 260.179       | 177.33     | 66.2792       |  |  |  |

| 17                                                         | s38584.1 | 91.00      | 150.017       | 101.1      | 53.75495      |  |  |  |

| 18                                                         | seq      | 140.00     | 153.597       | 126.938    | 19.04214      |  |  |  |

| 19                                                         | spla     | 120.00     | 212.304       | 135.31     | 64.16167      |  |  |  |

| 20                                                         | tseng    | 80.00      | 84.2235       | 90.0419    | -7.273        |  |  |  |

| Average                                                    |          |            |               |            | 26.85031      |  |  |  |

#### 4. CONCLUSION

Timing driven routing is a well-studied problem and important problem considering the impact of routing to performance of the design after fabrication. In this paper we present a timing driven routing algorithm. We present two methods for weighing the nets of critical path of a design. Our experiments show that an improvement of 14.65 % using Method A and 26.85% using Method B can be obtained. Our approach shows promising results over the well-known FPGA routing tool VPR.

## **ACKNOWLEDGEMENTS**

We would like to thank Department of Electronics and Communication Engineering, Cambridge Institute of Technology, Bangalore for providing the resources to conduct the experiments.

#### REFERENCES

- P. Tu, W. Chow and E. F. Y. Young, "Timing driven routing tree construction," 2017 ACM/IEEE International Workshop on System Level Interconnect Prediction (SLIP), Austin, TX, 2017, pp. 1-8.

- Dongsheng Wang and E. S. Kuh, "A new general connectivity model and its applications to timing-driven Steiner tree routing," 1998 IEEE International Conference on Electronics, Circuits and Systems. Surfing the Waves of Science and Technology (Cat. No.98EX196), Lisboa, Portugal, 1998, pp. 71-74 vol.2.

- Dongsheng Wang and E. S. Kuh, "A new timing-driven multilayer MCM/IC routing algorithm," Proceedings 1997 IEEE Multi-Chip Module Conference, Santa Cruz, CA, USA, 1997, pp. 89-94.

- Jin-Tai Yan, Chia-Fang Lee and Yen-Hsiang Chen, "A simulated-annealing-based approach for timing-constrained flexibility-driven routing tree construction," The 2004 47th Midwest Symposium on Circuits and Systems, 2004. MWSCAS '04., Hiroshima, Japan, 2004, pp. I-461.

- Tsung-Yi Ho, Yao-Wen Chang, Sao-Jie Chen and Der-Tsai Lee, "Crosstalk- and performance-driven multilevel full-chip routing," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 24, no. 6, pp. 869-878, June 2005.

- Fang-Jou Liu, J. Lillis and Chung-Kuan Cheng, "Design and implementation of a global router based on a new layout-driven timing model with three poles," Proceedings of 1997 IEEE International Symposium on Circuits and Systems. Circuits and Systems in the Information Age ISCAS '97,

- Jiang Hu and S. S. Sapatnekar, "Performance driven global routing through gradual refinement," Proceedings 2001 IEEE International Conference on Computer Design: VLSI in Computers and Processors. ICCD 2001, Austin, TX, USA, 2001, pp. 481-483.

- K. Roy, "Power-dissipation driven FPGA place and route under timing constraints," in IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 46, no. 5, pp. 634-637, May 1999.

- J. Monteiro et al., "Routing-Aware Incremental Timing-Driven Placement," 2016 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Pittsburgh, PA, 2016, pp. 290-295.

- Hsiao-Ping Tseng, L. Scheffer and C. Sechen, "Timing- and crosstalk-driven area routing," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 20, no. 4, pp. 528-544, April 2001.

- T. Deguchi, T. Koide and S. Wakabayashi, "Timing-driven hierarchical global routing with wire-sizing and buffer-insertion for VLSI with multi-routing-layer," Proceedings 2000. Design Automation Conference. (IEEE Cat. No.00CH37106), Yokohama, 2000, pp. 99-104.

- Sung-Woo Hur, A. Jagannathan and J. Lillis, "Timing-driven maze routing," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 19, no. 2, pp. 234-241, Feb. 2000.

- Jin-Tai Yan, Shi-Qin Huang and Zhi-Wei Chen, "Top-down-based timing-driven steiner tree construction with wire sizing and buffer insertion," TENCON 2007 - 2007 IEEE Region 10 Conference, Taipei, 2007, pp. 1-4.

- C. Alexandre, H. Clement, J. -. Chaput, M. Sroka, C. Masson and R. Escassut, "TSUNAMI: an integrated timing-driven place and route research platform," Design, Automation and Test in Europe, Munich, Germany, 2005, pp. 920-921 Vol. 2.