# Modelling of DVR with Artificial Intelligence for Compensate the Voltage Sag, Swell and Flickers by Using SVPWM Switching Techniques in Distribution Lines

# N.Eashwaramma, J.Praveen, M.VijayaKumar

Abstract: In this research proposes FLC and Artificial Neural Network (ANN) based on Dyanamic Voltage Controller (DVR) along with d q o transformation for power qulity improvement in a distribution system. Design a 9levels CHMLI based on Custom Power device with SVPWM techniques. Distribution needs to protect against the harmonics such as sag, swell and flickers are affect on standard pure power supply at the end of the load. These power quality issues are minimised with voltage injection using DVR.The designed inveter to reduced the voltage switching losses and stresses of semiconductor devices. Here used single DC voltage source with a series connection of 4 capacitors for self balancing purpose, 3 diodes, output voltage levels and Cascaded H-bridge cell. the proposed 9 level CHMLI inverter citcuit to helps reducing the number of independent voltage dc sources and IGBTS. The harmonics are less in the output voltage proposed work (new topologies)compared to conventional topology. A comparision of FLC and ANN with THD and Power Factor results and study. It has been carried out to analyse through MATLAB / SIMULINK Software.

Keywords: DVR, 9 level CHMLI, SAG, SWELL, Flickers, PF, THD, FLC, ANN and SVPWM.

#### I. INTRODUCTION

Todays pure quality of power the most important issues are in the society and companies. It is highly competitive in society, it affects the benefits of both of time periode and economy. These are needed to demand for pure quality of power. Industries are used of modern devices and new technologies such as sensitive devices are

semiconductor devices, Programmable Logic Controller (PLC) and Power electronice devices these devices have given quality of power problems (1) (reference by Maalmargun Jayabalan, Thamizharasan in 2016 IET Power Electronics) such as harmonics like voltage sag, Swell and voltage flickers etc. These issues are severe disturbances in distribution system.

Voltage sag is "decrease in rms ac voltage between 10% and 90% frequency for durations from 1/2 cycles to one minute" and voltage swell as an increase in rms ac voltage greater than 110% and 180% frequency for a duration longer than 1min(2,3).

Revised Manuscript Received on April 02, 2020.

\* Correspondence Author

N.Eashwaramma\*, Research scholar JNTUA,

**Dr.J.Praveen,** Profeesor in GRIET, Dept EEE, Affiliation JNTUH Hyderabad

Dr.M.VijayaKumar, JNTUA, Dept.EEE, Ananthapuramu,India

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/)

(N.G.Hingorani, IEEE pectrum,

Md.IltafISSN:23218169Volume:3Issue:2132-136

32IJRITCC | February 2015) Power quality issues are occurs in the power systems field like voltage Sag, voltage swell and Flickers in with magnitude and time duration.(4) (reference

by Arash Khoshkbar Sadigh Seyed Hossein Hosseini, Mehdi Fara sat, Ehsan Mokhtar pour Faculty of Electrical and Computer Engineering, University of Tabriz, Tabriz, Iran 1 st Power Electronic & Drive Systems & Technologies Conference)

The FACT device is a DVR. It is modified as per customers requirements that is called custom power device, which provides a more efficient and fast dyanamic solution to quality of power issues. It a compensated the voltage harmonics sag and swell.(5) (referece byKantaria,R.A.;Joshi,S.K.;Siddhapura,K.R.Electro/Informa tion Technology (EIT), 2010 IEEE International Conference on, vol., no., pp.1,4, 20-22 May 2010). Control unit(CU) is that main part of the DVR function is to find quality of power issues in this system and calculating the required injecting and generate the reference voltage for PWM generate to switching IGBTs of inverter.(6)(reference by Prof R. Kameswara Rao , 2,P. Srinivas , 3,M.V. Suresh Kumar. Science (IJES) ISSN (e): 2319 - 1813 ISSN (p): 2319 – 1805 Pages (41-51 ) 2014.)

The FLC (Fuzzy Logic cotrollers) and Neural Networks(NN) have obtained good applications. FLCs advantages of over conventional controllers, its does give accurate value but time duration is very less., Its work on inputs can handle non linearity and non linear controllers. This controller needs many membership functions, some other researchers have been to decrease the number of or nonlinear functions or membership functions. A FLC controller is introduced with proposed technique to enhance the effectiveness and robustness in compensating the missing voltage. (7) ('reference by Harish suryanarayana et al. An improvement of transient performance of the dc link by FLC based method and PI Controller and Fuzzy Logic Controller based dc capacitor voltage is regulator was analysed.') In this research work the DVR with proposed control technique is implemented in a suitable best test system with linear load considering issues in this systems.

ANNs(Artificial Neural Network) the results of investigations that use mathematical formulations to model nervous systems operations. The resulting techniques were being successfully applied in a variety of every day different business applications.

NNs reperesent a meaningfully different approaches of using computers in the work place. A neural network is used to learn patterns and relation ship in the data. Regardless of the specific involved, applying neural network(NN) is substantially different from traditional approaches. Traditional programmer or analyst specifically "codes"for every facet of the problem for computer to "under stand"the situation. NN does not required explicit coding of the problem. Artificial Neural Network(ANN) started 50 years ago and it was invented by Rosen Blatt. ANN, THD and Power Factor results good compared to FLC results.

### II. MULTI LEVEL INVERTER(MLI)

MLI is made with power electronic circuits which its converts dc power to ac power at desired output voltage and frequency at different multilevel. The proposed circuit developed based on conventional type of MLI. The proposed method is known as new topology or reduction technique. Its designed with 24 IGBTS, 3DC sources and capacitors for self balancing purpose. This inverter system generated low harmonics compared to the conventional types of inverters.

The conventional type inverter which operates at high frequency, high harmonic distortion and high voltage stress, from these disadvantages are compensated by introduced a new topology i.e called 9 level Cascaded H-bridge Multi Level Inverter(reduction technique). By this new topology is used to overcome the disadvantages by increasing the power rating of the device. The advantages of reduction technique of cascaded the multilevel inverters are as follows:

- 1. Inverter output, increase in the number of voltage levels.

- 2. Decrease the harmonics in Inverter output (Injecting voltage).

- 3. Switching losses are less as well as voltage stress also decreases.

- 4. Output waveform of MLI in the stair case model.

- 5. It is used for High power applications

When compared THD and Power factor results of conventional topology (three phase three legs 9 levels CHMLI, 48 IGBTs) and the proposed topology of nine level CHMLI (three phase three legs 9 levels CHMLI, 24 IGBTs). As per these results the proposed topology is best method. Proposed topology advantages are like 3 dc source, less number of IGBTS, low switching losses, capacitors are used for self-balanced voltage purposeand less harmonic content in compensating voltage.

**Fig1: One leg of CHMLI (used 8 switches)** Figure 1 Circuit working as per below table 1.

Table1: Switching table for proposed nine level inverter

| Switches Turn on | Voltage level |

|------------------|---------------|

| S1,S5,S8         | Vdc           |

| S2,S5,S8         | Vdc/4         |

| S3,S5,S8         | 2Vdc/4        |

| S4,S5,S8         | 3Vdc/4        |

| S7,S8            | 0             |

| S1,S6,S7         | -Vdc          |

| S2,S6,S7         | -Vdc/4        |

| S3,S6,S7         | -2Vdc/4       |

| S4,S6,S7         | -3Vdc/4       |

#### III. DYANAMIC VOLTAGE RESTORER(DVR)

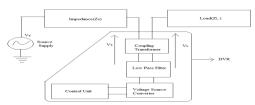

Fig2: Schematic diagram of DVR

Fig2 is called DVR block diagram and its consists of an Coupling Transformer, Low pass filter (LPF), Voltage Source Inverter(VSI), Control Unit(CU). The two main aim of Coupling Transformer of the DVR, first one connected to the disribution networks and second one compensating voltage from VSC i.e injected in to the disribution network. The main aim of low pass filter is eliminating the harmonic in the compensating voltage. The use of energy storage devices is to supply the necessary energy to the Voltage Source Inverter. A VSI is a power electronic device consists of a storage device and switching devices. This device is produce the sinusoidal with required magnitude of frequency and phase angle. The dyanamic voltage resorer first important task compensation of voltage Sag, voltage Swell and voltage Flickers. Reduction technique of CHMLI is developed in VSC.

## IV. CONTROL TECHNIQUE

The controller rules are DVR to detect the harmonics occurs in the distribution lines. These controllers generate the signals are to send to the pulse width modulation generator for generated the triggering pulses. These pulses are giving to the Inverter circuit of VSI. The DVR produced the compensating voltage by injecting the distribution lines for reducing the harmonics. In this research work, the d- q-o park transformation is used for voltage calculation.

The d-q-o is a transformation of co-ordinate from these 3 phase constant co-ordinate.(10) ( reference by Omar, R.; Rahim, N.A. 2008. AUPEC '08. Australasian Universities, vol., no., pp.1,5, 14- 17 Dec. 2008.).

This dqo method gives the information of the direct axes and shift of phase (q) or quadrature axes. This d- q-o method to give the information, the direct axes 'd' and quadrature axes 'q'.

$$\begin{split} V_0 &= \frac{1}{3} (\ V_a + V_b + V_c) \\ V_d &= \frac{2}{3} (\ V_a \sin(\omega t) + V_b \sin(-2\pi/3) \\ &+ V_c \sin(\omega t + 2\pi 3) \\ V_q &= \frac{2}{3} (V_a \cos(\omega t) + V_b \cos(\omega t - 2\pi/3) \\ &+ V_c \cos(\omega t + 2\pi 3) \omega t \end{split}$$

After convertion, the 3Ø voltage  $V_a$ ,  $V_b$  and  $V_c$ , which are converted in to both constant voltages are of the  $V_d$  and  $V_q$  and these are controlled easily.(11)( International Journal Of Engineering And Science (IJES) ISSN (e): 2319 - 1813 ISSN (p): 2319 - 1805 Pages (41-51) 2014 . American J. of Engineering and Applied Sciences 3 (1): 42-48, 2010 ISSN 1941-7020©2010Science.Publications Corresponding Author : Rosli Omar, Faculty of Electrical, Technical University Malaysia Malacca).In this research work three controlles are proposed, which are PI, FLC and ANN.

## A) Fuzzy Logic Controller (FLC)

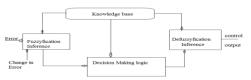

The FLC is the most important operations of fuzzy set theory, it is used major features of linguistic variables rather than numerical variables. This Control technique is understand the systems behaviour and based on quality control rules. FLC provides definite conclusion based upon vague. ambiguous, imprecise, noisy or missing input information.(13)(reference by Fuzzy logic and Neural Networks introduced by Chennakasesava R.Alavala about basic concepts and applications) Below figure3 is a basic structure of FLC.

Fig 3 Basic structure of FLC

- A Fuzzyfication inference: It converts input data into suitable different variables of linguistic values or membership functions.

- A knowledge base: which consists of a data base with the necessary linguistic definations and control rule set.

- A Decision making logic: which simulating a human decision process infers the fuzzy control system from the knowledge of the control rules and linguistic variables definations and

- ADefuzzyfication interface: which yields a nonfuzzy control action from an inferred fuzzy control action.(14) (referenceby K.Vijaya Baskar and satish IJARE 2015, vol 4,ISO 3297)

In this research work has two Fuzzy logic controller blocks are used for error signal - q.

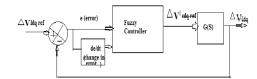

Error and change in error are the inputs to the fuzzy controller are shown in below fig4

Fig4: Feedback control loop of DVR

Fig 5: Membership function input variables "Error"

Fig6: Membership function input variables "Error rate"

Table 2: Decision table for logic control (Member functions.)

|       |    | Error rate |    |    |    |    |    |    |

|-------|----|------------|----|----|----|----|----|----|

| Error | 7  | LP         | MP | SP | S  | SN | MN | LN |

|       | LP | РВ         | РВ | PB | PM | PM | PS | Z  |

|       | MP | PB         | PB | PM | PM | PS | Z  | NS |

|       | SP | PB         | PM | PM | PS | Z  | NS | NM |

|       | S  | PM         | PM | PS | Z  | NS | NM | NM |

|       | SN | PM         | PS | Z  | NS | NM | NM | NB |

|       | MN | PS         | Z  | NS | NM | NM | NB | NB |

|       | LN | Z          | NS | NM | NM | NB | NB | NB |

From Table2 shown member functions LP =low positive,MP=Medium positive, SP = small positive,S=small,SN=Small negative MN= medium negative and LN=low negative. Above Member ship functions are 8 \* 8 matrix, there are 49 rules.

There are two types of methods of Fuzzy logic controller, which are Mamdani and Sugenio method. In this research work Mamdani method is used. This method suitable for nonlinear loads.

#### C) Artificial Neural Network

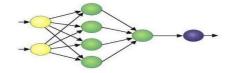

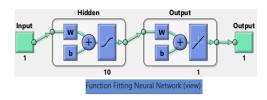

There are two methods of Artificial neural networks are feed forward and back forward network. In this research work feed forward method is used.

Fig7: Feed forward network

A neural network consists of a set of processing nodes, connected together. The connections bear weight whose value is adjusted during the process of training and is fixed after the training is over. These nodes can be arranged in two (input and output) or (hidden) layers.

# Modelling of DVR with Artificial Intelligence for Compensate the Voltage Sag, Swell and Flickers by Using SVPWM Switching Techniques in Distribution Lines

Each node receives input information either from an external source or from other nodes in the net shown in fig5. The input that any node receives from previous one is a function of the output of that node and weight of the connection between those two nodes. If there is more than one input to a node they all are combined in a particular manner to produce the corresponding output. The architecture of an ANN is decided by the arrangement of nodes and their interconnections in the network. Each node has activation value. The input to node and current state of activation are passed through a function 'f'to produce an ouput value for the node. After fixing the architecture for a specific neural network, set of input information and the corresponding known output information are fed at its input layer and the output nodes respectively. The initial weights and biases are arbitrary chosen and the network is trained. An algorithmic computation is carried out during training by which the network adjusts the weights and the threshold values such that error the error between the targeted output and the actual output and matches the predecided error goal. While training the weight and bias attributes get readjusted so as to produce the desired output values. The weights and the biases are then memorized and the network is then used to simulate new output corresponding to the given changes in the values. The network thus establishes an input and output mapping.

The process of learning that is the process of adjustment of the weights and the thresholds, however, requires a specific algorithmic approach. A variety of learning algorithms are available for training a network statistical soundness of training data, the network structure and the size of the neural network, number of hidden layer neurons, initial weights and biases and the learning strategy affect the accuracy of the results obtained through ANN.(15,16) (reference by John McCrthy was a father of Artificial Intelligence. E.A Mohamad, ND.D.Rao by Electrical power systems research detailed explained in 1995)

# V. SIMULATION DIAGRAMES WORKING EXPLANATION

In this paper designed nine level Cascaded Hybrid Multivevel Inverter (CHMLI) for compensated Voltage Sag, Swell and Flickers based on dyanamic voltage vector pulse width controller (DVR) using space modulation(SVPWM) techniques. SVPWM techniques results more efficient compared to sinusoidal pulsewidth modulation(SPWM) technique. The conventional type of nine level CHMLI used 48 IGBTS and 12 DC Sources. This type MLI, dis advantages are cost is high, occupied space area more and more number of harmonics are generated. These disadvantages are reduced by developed new technique that is a "Reduction technique or new topology". It is developed with nine CHMLI and desgned with 24 IGBTS, 3 DC Sources and 12 capacitors are connected in series for self balanced voltage purpose. This new topology advantages are reduced number of power switches, dc sources, reduced switching losses, the voltage stresses of power devices ande occupied space area and cost. The harmonic contents are in the output voltage is very less in reduction technique, when compared to the conventional type CHMLI. The proposed topology is verfied by using Matlab / simulink software. ANNs applied to new topology to measured THD from FFT Analysis and PF results. ANNs results perfect results shown in table 3 compared FLC controller.

#### VI. SIMULATION RESULTS

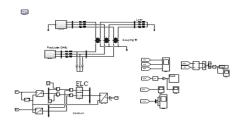

Fig9:Main circuit diagram of 9 level reduction technique of CHMLI based on DVR using SVPWM with FLC Controllers for compensated voltage Sag, Swell and Flickers.

For above fig9 main simulation diagram of 9 level CHMLI based on DVR using SVPWM with FLC controllers for compensated voltage Sag, Swell and voltage flickers. From this above figure created voltage sag, swell and voltage flickers because of three phase fault, large load additions, power line switching. In above diagram small frequency disturbance created in the source supply causes in flickers. DVR Consists of Control unit, VSC, Low pass filter and Coupling T/F. FLC and SVPWM methods are designed in control unit. These techniques are generated to control signals to give PWM methods for generating triggering pulses for switching to the power switches (IGBTS) of VSC. In VSC, designed reduction technique of 9 level CHMLI. This type of reduction technique generated compensating voltage with low harmonics. low switching losses. 9 level CHMLI reduction model is used 24 IGBTS, its gives more advantages are low cost, occupied space is very less and fast dynamic solution. The simulation diagrams generated low THD % = 0.8 and Power factor = 0.9762. Fuzzy logic technique is used in main diagram for improved the performance of the DVR. Combination of FLC with SVPWM method is suitable for generating low harmonics.

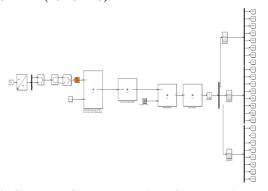

Fig10: Main circuit diagram of 9 level reduction type CHMLI based on DVR using SVPWM with ANN Controllers for compensated voltage Sag, Swell and Flickers.

For 10 simulation diagram of 9 level CHMLI reduction type based on DVR using SVPWM with ANN Controllers for compensated voltage Sag, Swell and Flickers.

ANN method is excellent method compared to FLC and PI Controllers. In ANN method is doing testing and training finally get Function fitting neural network block. Function fitting neural network block placed in place of FLC controller in above figure 10. This type of method generated less harmonics and it gives accurate values, but sampling time is more compared to FLC Controllers. Where above diagram generated THD%=0.36 and Power Factor=0.9997. This figure is called Power quality circuit. Finally this circuit is generated low harmonics, less occupied space area, less cost and simple circuit.

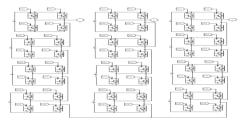

Fig 11. Nine level CHMLI, Conventional type (using 48 IGBTS) using SVPWM with fuzzy logic and ANN

This circuit diagram is called as three phase three legs 9 level CHMLI. This circuit is called conventional type, it is used 48 switches (IGBTS), 12 DC Sources and 12 H-Bridges. Circuit cost is more, space area also more but its generated harmonics are less.

Fig12 Nine level CHMLI New topology(24 IGBTS) (reduction technique) (In this case using SVPWM fuzzy logic and ANN)

This circuit diagram is called reduction method, it is designed with 24 IGBTS, 3 DC sources 3 H-Bridges, Capacitors for self balancing purpose and diodes. This circuit diagram cost is less, less occupied space area and generated harmonics are low compared to the conventional type CHMLI (48 IGBTS).

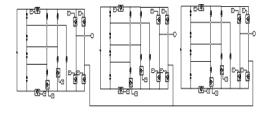

Fig9: SVPWM Control technique for reduction type 9 level CHMLI

Retrieval Number: D7572049420/2020©BEIESP DOI: 10.35940/ijeat.D7572.049420 Journal Website: www.ijeat.org

[1x16] [1×16] [1×16] [1×16]

Fig13: Switch Selector (SVPWM)

Fig14: Using Fuzzy Logic Controller

Detailed explained in B) fuzzy logic section above.

Fig15: Neural network subsysytem

In this research work consider 10 hidden layers and one input and one out put so it is called fedd forward method ."W" is called weight and "b " is called bias.

Fig16: Fuction fitting Neural Network

Figure 14 is fuzzy logic in this diagram replaced by Fig16: Fuction fitting Neural Network, so it is called ANN.

Fig17. ANN Weights and hidden layers diagram

Fig17, displayed ten(10) hidden layers are used these layers are associated with weights. These all weights are adding in function of final node that activation node.

Fig18: Vector diagram of SVPWM for 9 level CHMLI

Fig18 is known as space vector for 9 level CHMLI. X axis is called direct axis ,it is reperesnts d or alpha and Y axis is called quadrature axis it is represent q or beta. This space vector designed as per nine levels. It shows vectors and sectors. Vector is knowns magnitude and phase ,these are applied to source voltage when sag, swell and harmonics occurs.

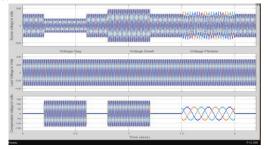

Fig19: Wave forms of Voltage sag, swell, Flickers, constant load voltage and injected voltage

Fig 19 displayed three figures, first figure is shown Voltage sag, swell and Flickers. These are occurs in three phase distribution lines because of faults, large load additions, power line switching, at homes used Current heaters and Washing

machines. Voltage sag and swell harmonics are very harmful in distribution lines and Flickers are occurs very less or rarely. Second figure is called constant load voltage. Reduction method is generated very few or low harmonics. In load voltage observed low harmonics. This type of voltage or standard voltage supplied to the near the consumer places or loads, sensitive equipment life span reduced the damages. Third figures and represents compensating voltage, its generated by DVR to injecting in to the distribution lines through Coupling Transformer and low pass filter so maintained constant load voltage.

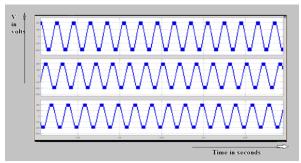

Fig20: output wave forms of 9 levels CHMLI **Total Harmonic Distortion(in %)**

$$V_{THD} = \frac{\sqrt{\sum_{n=2}^{\infty} V_n^2}}{V_1}$$

Where

Vn = RMS voltage nth harmonic

V1 = RMS voltage of the fundamental frequency

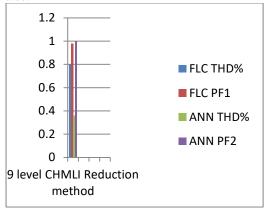

Table3: THD and PF Results of topology of 9 levels CHMLI (compensated Voltage sag, swell and Flickers)

|                          |     | 9 level<br>CHMLI<br>Topology method<br>(reduction method)<br>(24 IGBTS) |

|--------------------------|-----|-------------------------------------------------------------------------|

| With<br>Fuzzy(S<br>VPWM) | THD | 0.8                                                                     |

|                          | PF  | 0.9762                                                                  |

| With<br>ANN              | THD | 0.36                                                                    |

| (SVPW<br>M)              | PF  | 0.9997                                                                  |

From Table3 Observed the THD and Power factor results. The ANN THD and Power Factor results best compared to FLC. In this research work designed reduction type 9 levels CHMLI that is new topology. Conventional method is used 48 IGBTS and this method generated more harmonics and power factor is very poor. Designed reduction type circuit has 24 IGBTS, this circuit generated low harmonics, good power factor, occupied less space, low cost and generated low switching losses. As per Table3 results, Reduction method is excellent method for future scope also.

Figure 21: Barcode for comparison of FLC and ANN of reduction method.(compensated Voltage sag, swell and Flickers)( used24 IGBTS)

From above Barcode diagram, Reduction technique with ANN generated less THD%= 0.36 and Power Factor = 0.9997 compared to Reduction technique of FLC, its generated THD% = 0.8 and Power Factor = 0.9762. ANN technique is excellent technique compared to convention method.

Published By:

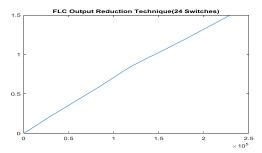

Fig22: Output signal of FLC using SVPWM

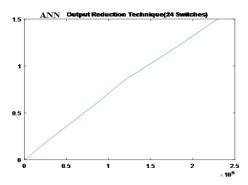

Fig23: Output signal of ANN using SVPWM

From above figure 22 and figure 23, observed that the Signal curve of ANN using SVPWM technique is pure compared to output of curve FLC. From above two diagrams ANN technique is gives accurate values and it is a best method compared to FLC method.

#### VII. CONCLUSION

In this research work, Simulation of reduction type of 9 level CHMLI based on DVR is developed. In this paper design reduction method(new topology) of MLI, i.e IGBTs are reduced to 24 IGBTs. This new topology technique is good performance compared to Conventional type(48 switches) of CHMLI. Advantages of new topology reduced space area, cost, harmonics and good Power factor. The DVR has been simulated with SVPWM techniques. Artificial Neural Network results good compared to Fuzzy logic Controller of CHMLI of reduction method. In this research work simulation diagrams for help compensated the quality of power issues like voltage sag, swell and flickers in three phase electrical distribution lines for improvement the quality of power. This research work proposed the enhancement of power transfer capability and maintaining good power factor.

#### REFERENCES

- Maalmargun Jayabalan, Thamizharasan "A new reduced switch count pulse width modulated multilevel inverter" published in IET, PowerElectronics in 2016, Page no 1-24.

- N.Nagalakshmi U. Ramesh Babu, Syed Munvar ali, K.Sudheer "A Single Phase Nine Level Inverter with reduced switches" published in IEEE International Conference on power, control, signals and Instrumentation Engineering (ICPCSI 2017)

- Dr.S.Chenthur Pandian, Dr. Mahalingam, R.Karthikeyan "An Efficient Multilevel Inverter System for Reducing THD with Space Vector Modulation" International Journal of Computer Applications (0975 – 8887) Volume 23 – No.2, June 2011

- Omar, R.; Rahim, N.A., "Modeling and simulation for voltage sags/swells mitigation using dynamic voltage restorer (DVR)" Power Engineering Conference, 2008. AUPEC '08. Australasian Universities, vol., no., pp.1,5, 14-17 Dec. 2008.

- Rosili Omar,." Modelling and simulation of a thre phase MLI for harmonics reduction based on modified svpwm" Journal of Theoretical and Applied Information Technology, 20th July 2015. Vol.77. No.2,© 2005 - 2015 JATIT & LLS. All rights reserved.

- E.A Mohamad ,ND.D.Rao by "Artificial Neural Network based fault diagnostic system for electric power distribution feeders" Electrical power systems research detailed explained in 1995.

- Arindam Gosh and Gerarad ledwich Text book , Clearly. Jin-Lung, Ming-Tayang in 2007 "presented about Flickers, voltage Flickers is mainly caused by rapid change of loads in power systems". page no.417 to 421 [37]

#### **AUTHOR PROFILE**

N.Eashwaramma.B.Tech(EEE) ,M.Tech (Ph.D) I did B.Tech from GNITS and M.Tech from JNTUH Hyderabad and I am pursuing Ph.D in the field power Electronics from JNTUA,Anantapuram. (AP)

Main\_ supervisor :Dr. J. Praveen B.E(EEE),

M.Tech, Ph.D Principal of GRITS and professor

in EEE dept. Graduate from Osmania university

college of Engineering(Autonomous)in EEE

Hyderabad. He has done Masters from

Jawaharlal Nehru Technological University

Hyderabad, He has Doctrate in philosophy in

from Osmania university in the field of power

Electrical Engineering Electronics.

Co-supervisor:

Dr.M.VijayaKumar, M.Tech,Ph.D,Professor &Register of JNTUA, professor in EEE Dept. 30 years teaching experience and 25 years research experience. Publications:Journals, international and national 60 and Conferences :international and national 63. Research Areas:Power Electronics & Industries